- Overview

- The Ethernet Media Access Controller (GRETH) provides an interface between an AMBA-AXI bus and Ethernet network. It supports 10/100 Mbit speed in both full- and half-duplex modes. Integrated EDCL submodule implements hardware decoding of UDP traffic and redirects EDCL request directly on AXI system bus. The AMBA interface consists of an AXI slave interface for configuration and control and an AXI master interface for transmit and receive data. There is one DMA engine for the transmitter and one for receiver. EDCL submodule and both DMA engines share the same AXI master interface.

To make development board visible in your local network your should properly specify connection properties. In this chapter I will show how to configure the host computer (Windows 7 or Linux) to communicate with the FPGA hardware over Ethernet.

- Note

- If you also want simultaneous Internet access your host computer requires a second Ethernet port. I couldn't find workable configuration via router.

- Warning

- I recommend you to make restore point before you start.

Configure Windows Host

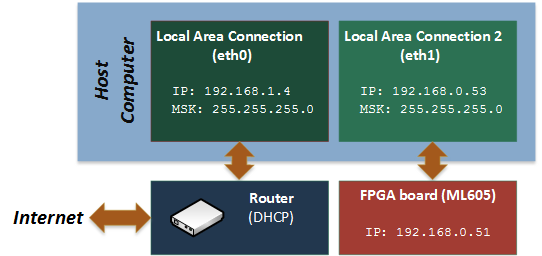

Let's setup the following network configuration that allows to work with FPGA board and to be connected to Internet. I use different Ethernet ports and different subnets (192.168.0.x and 192.168.1.x accordingly).

- Host IP and subnet definition:

- Open

cmd console.

- Use

ipconfig command to determine network settings. ipconfig /all

- Find your IP address (in my case it's 192.168.1.4)

- Check and change if needed default IP address of SOC as follow.

- Setup hard-reset FPGA IP address:

- Open in editor rocket_soc.vhd.

- Find place where grethaxi module is instantiated.

- Change generic ipaddrh and ipaddrl parameters so that they belonged another subnet (Default values: C0A8.0033 corresponding to 192.168.0.51) than Internet connection.

- Configure the Ethernet card for your FPGA hardware

- Load pre-built image file into FPGA board (located in ./rocket_soc/bit_files/ folder) or use your own one.

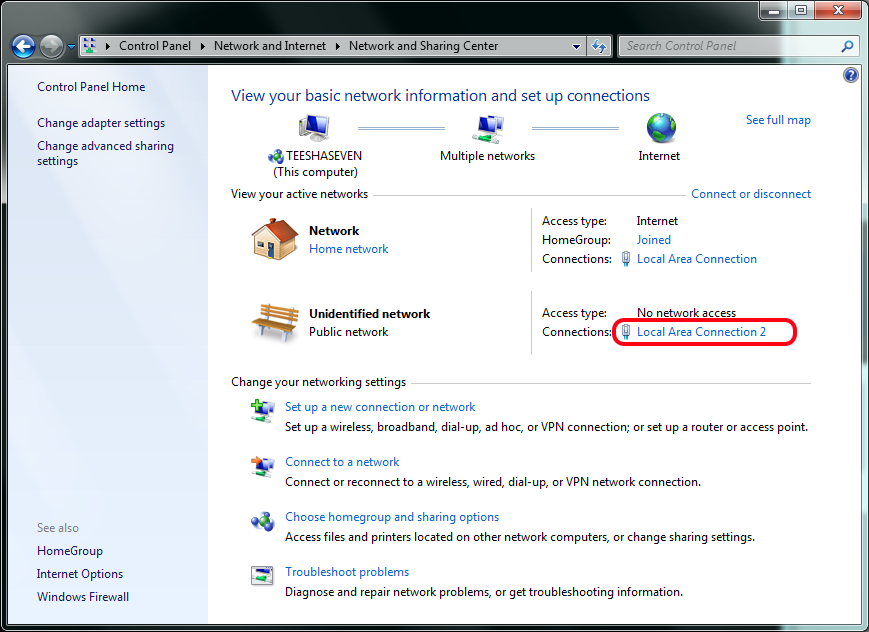

- Open Network and Sharing Center via Control Panel

-# Click on <b>Local Area Connection 2</b> link

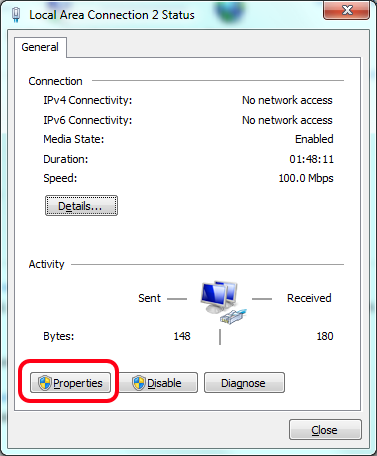

-# Click on <b>Properties</b> to open properties dialog.

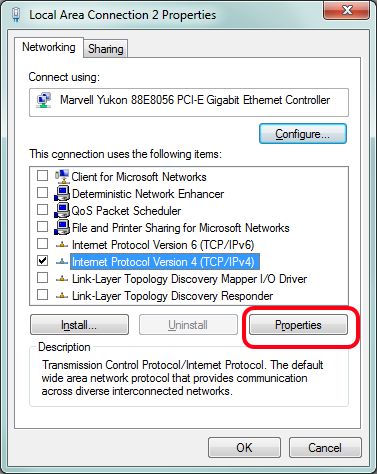

-# Disable all network services except <b>Internet Protocol Version 4</b>

as shown on figure above.

- Select enabled service and click on Properties button.

-# Specify unique IP as shown above so that FPGA and your Local

Connection were placed in the same subnet.

- Leave the subnet mask set to the default value 255.255.255.0.

- Click OK.

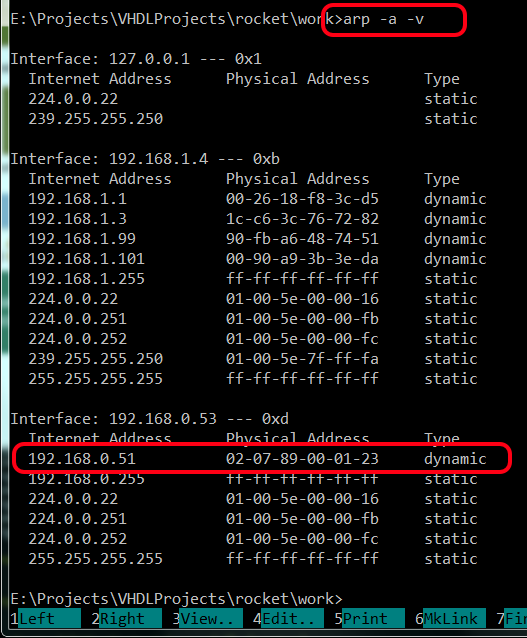

- Check connection

- Check presence of the Ethernet activity by blinking LEDs near the Ethernet connector on FPGA board

- Run

arp command to see arp table entries. arp -a -v

-# MAC supports only ARP and EDCL requests on hardware level and it cannot

respond on others without properly installed software. By this reason ping won't work without running OS on FPGA target but it maybe usefull to ping FPGA target so that it can force updating of the ARP table or use the commands:

ipconfig /release

ipconfig /renew

Configure Linux Host

Let's setup the similar network configuration on Linux host.

- Check ipaddrh and ipaddrl values that are hardcoded on top-level of SOC (default values: C0A8.0033 corresponding to 192.168.0.51).

- Set host IP value in the same subnet using the

ifconfig command. You might need to enter a password to use the sudo command. % sudo ifconfig eth0 192.168.0.53 netmask 255.255.255.0

- Enter the following command in the shell to check that the changes took effect:

% ifconfig eth0

Run Application

Now your FPGA board is ready to interact with the host computer via Ethernet. You can find detailed information about MAC (GRETH) in GRLIB IP Core User's Manual.

There you can find:

- DMA Configuration registers description (Rx/Tx Descriptors tables and entries).

- EDCL message format.

GRLIB itself includes C-example that configure MAC Rx/Tx queues and start transmission of the 1500 Mbyte of data to define Bitrate in Mbps.

We provide debugger functionality via Ethernet. See Debugger description page.