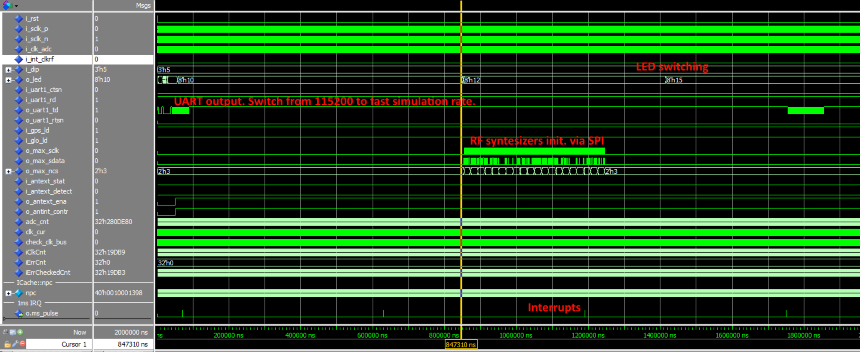

Some FW versions can detect RTL simulation target by reading 'Target' Register in PnP device that allows to speed-up simulation by removing some delays and changing Devices IO parameters (UART speed for example).

Edit the following attributes in SystemC target script debugger/targets/sysc_river_gui.json to enable vcd-file generation.

Files i_river.vcd and o_river.vcd will be generated. The first one will be used as a RTL simulation stimulus to generate input signals. The second one as a reference.

Run simulation in ModelSim with the following commands using correct pathes for your host:

vcd2wlf E:/Projects/GitProjects/riscv_vhdl/debugger/win32build/Debug/i_river.vcd -o e:/i_river.wlf vcd2wlf E:/Projects/GitProjects/riscv_vhdl/debugger/win32build/Debug/o_river.vcd -o e:/o_river.wlf wlf2vcd e:/i_river.wlf -o e:/i_river.vcd vsim -t 1ps -vcdstim E:/i_river.vcd riverlib.RiverTop vsim -view e:/o_river.wlf add wave o_river:/SystemC/o_* add wave sim:/rivertop/* run 500us compare start o_river sim compare add -wave sim:/RiverTop/o_req_mem_valid o_river:/SystemC/o_req_mem_valid compare add -wave sim:/RiverTop/o_req_mem_write o_river:/SystemC/o_req_mem_write compare add -wave sim:/RiverTop/o_req_mem_addr o_river:/SystemC/o_req_mem_addr compare add -wave sim:/RiverTop/o_req_mem_strob o_river:/SystemC/o_req_mem_strob compare add -wave sim:/RiverTop/o_req_mem_data o_river:/SystemC/o_req_mem_data compare add -wave sim:/RiverTop/o_dport_ready o_river:/SystemC/o_dport_ready compare add -wave sim:/RiverTop/o_dport_rdata o_river:/SystemC/o_dport_rdata compare run

vcd2wlf and wlf2vcd utilities to form compatible with ModelSim VCD-file. Otherwise there're will be errors because ModelSim cannot parse std_logic_vector siganls (only std_logic).