- Overview

- The IP Library is an integrated set of reusable IP cores, designed for system-on-chip (SOC) development. The IP cores are centered around a common on-chip AMBA AXI system bus, and use a coherent method for simulation and synthesis. This library is vendor independent, with support for different CAD tools and target technologies. Inherited from gaisler GRLIB library plug&play method was further developed and used to configure and connect the IP cores without the need to modify any global resources.

- Library organization

- Open source repository with VHLD libraries, Debugger, SW and debugger is available at:

https://github.com/sergeykhbr/riscv_vhdl

This repository is organized around VHDL libraries, where each major IP is assigned a unique library name. Using separate libraries avoids name clashes between IP cores and hides unnecessary implementation details from the end user.

- Satellite Navigation support

- Hardware part of the satellite navigation functionality is fully implemented inside of the gnsslib library. This library is the commercial product of GNSS Sensor limited and in this shared repository you can find only: modules declaration, configuration parameters and stub modules that provide enough functionality to use SOC as general purpose processor system based on RISC-V architecture. Netlists of the real GNSS IPs either as RF front-end for the FPGA development boards could be acquires via special request.

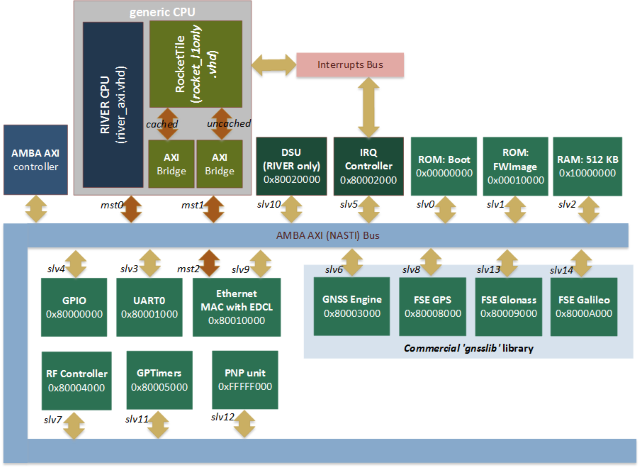

- Common Top-level structure

- Features

-

Pre-generated single-core "Rocket-chip" core (RISC-V). This is 64-bits processor with I/D caches, MMU, branch predictor, 128-bits width data bus, FPU (if enabled) and etc.

-

Custom 64-bits single-core CPU "River"(RISC-V).

-

Set of common peripheries: UART, GPIO (LEDs), Interrupt controller, General Purpose timers and etc.

-

Debugging via Ethernet using EDCL capability of the MAC. This capability allows to redirect UDP requests directly on system bus and allows to use external debugger from the Reset Vector.

-

Debug Support Unit (DSU) for the RIVER CPU with full debugging functionality support: run/halt, breakpoints, stepping, registers/CSRs and memory access. Also it provides general SoC run-time information: Clock Per Instruction (CPI), Bus Utilisization for each master device and etc.

-

Templates for the AXI slaves and master devices with DMA access

-

Configuration parameters to enable/disable additional functionality, like: GNSS Engine, Viterbi decoder, etc.

Information about GNSS (Satellite Navigation Engine) you can find at www.gnss-sensor.com.

VHDL Generic Parameters

RTL Verification

RISC-V Processor

Peripheries

RISC-V debugger